X68ブログ

サイト「X68000改造室」http://x68.aikotoba.jp の更新告知やサイト運営、X68の改造にまつわる小ネタを書いていきます。また、コメントを通して、サイトを見ていただいた方との交流の場ともしていきたいと思います。感想や疑問、記事の誤りなど、コメントいただければ、記事に反映していきたいと思います。

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

VHDLソース修正は続く

あけましておめでとうございます。

スキャンコンバータのソースの見直しをしています。外部クロックを逓倍するDCMのX68000起動時や解像度モード切り替え時の挙動をなんとかしようとしましたが、なかなか効果ある対処ができませんでした。そこで、発想を変え、DDR2メモリへまずはどんな解像度のものもそのままキャプチャさせ、表示側で水平解像度変更を行わせることにしました。

SVGAのピクセルクロックは40MHzですが、今度はこれの1/1.5、1/3の周波数のクロックを使ってDDRのメモリを読み出し表示させるのです(水平・垂直同期はSVGAのままに固定)。

で、外部クロックとは違い、安定したクロック50MHzでまずは1/1.5のクロックを作り動作試験をしました。その時の出力画像はこちら。絵が斜めになっています。 なんでこうなるか考え、あれやこれや半日いじって、やっと正常に表示するようになりました。その対応記録です。

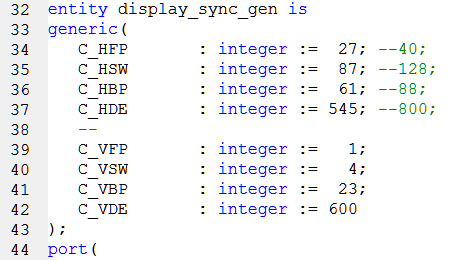

以下は表示タイミングを作る回路のVHDLソースの一部です。回路生成にあたって、ピクセルクロック換算で波形各部の長さを規定している部分で、SVGAのクロック40MHzの1.5分の1(正確にはDCMで作り出せたのは27.273MHzだったので、1.4667分の1)に合わせ、値を修正したところです。

C_HDEが水平表示期間を示し、800を545に直しているのですが、画像がおかしくなったのは、これが1多かったのが原因でした。C_HDEを544に減らし、合計値を合わせるため、C_HBP(バックポーチ)を逆に1足して生成し直すと正しく表示してくれました。HDMIの方も正常に表示してくれました。

こちらの回路生成では、X68000の起動時から誤動作することなく、512X512の画像をSVGA画像にしてくれました。解像度モード切り替え対応に向けて一歩前進です。

★★★ メインサイトへのリンク 「X68000改造室」★★★

スキャンコンバータのソースの見直しをしています。外部クロックを逓倍するDCMのX68000起動時や解像度モード切り替え時の挙動をなんとかしようとしましたが、なかなか効果ある対処ができませんでした。そこで、発想を変え、DDR2メモリへまずはどんな解像度のものもそのままキャプチャさせ、表示側で水平解像度変更を行わせることにしました。

SVGAのピクセルクロックは40MHzですが、今度はこれの1/1.5、1/3の周波数のクロックを使ってDDRのメモリを読み出し表示させるのです(水平・垂直同期はSVGAのままに固定)。

で、外部クロックとは違い、安定したクロック50MHzでまずは1/1.5のクロックを作り動作試験をしました。その時の出力画像はこちら。絵が斜めになっています。 なんでこうなるか考え、あれやこれや半日いじって、やっと正常に表示するようになりました。その対応記録です。

以下は表示タイミングを作る回路のVHDLソースの一部です。回路生成にあたって、ピクセルクロック換算で波形各部の長さを規定している部分で、SVGAのクロック40MHzの1.5分の1(正確にはDCMで作り出せたのは27.273MHzだったので、1.4667分の1)に合わせ、値を修正したところです。

C_HDEが水平表示期間を示し、800を545に直しているのですが、画像がおかしくなったのは、これが1多かったのが原因でした。C_HDEを544に減らし、合計値を合わせるため、C_HBP(バックポーチ)を逆に1足して生成し直すと正しく表示してくれました。HDMIの方も正常に表示してくれました。

こちらの回路生成では、X68000の起動時から誤動作することなく、512X512の画像をSVGA画像にしてくれました。解像度モード切り替え対応に向けて一歩前進です。

★★★ メインサイトへのリンク 「X68000改造室」★★★

PR

カレンダー

フリーエリア

最新CM

[02/01 ぱち(管理人)]

[01/31 saku39]

[12/27 ぱち(管理人)]

[12/27 saku39]

[01/20 ぱち(管理人)]

最新記事

(01/13)

(12/31)

(12/30)

(11/26)

(11/25)

プロフィール

HN:

ぱち

性別:

非公開

ブログ内検索

最古記事

(01/13)

(01/19)

(01/20)

(01/21)

(01/22)

COMMENT