X68ブログ

サイト「X68000改造室」http://x68.aikotoba.jp の更新告知やサイト運営、X68の改造にまつわる小ネタを書いていきます。また、コメントを通して、サイトを見ていただいた方との交流の場ともしていきたいと思います。感想や疑問、記事の誤りなど、コメントいただければ、記事に反映していきたいと思います。

カテゴリー「X68000」の記事一覧

- 2026.03.31 [PR]

- 2015.01.02 VHDLソース修正は続く

- 2014.12.30 Web記事アップ

- 2014.12.28 ユニバーサルボード

- 2014.12.25 XVI基板の改造完了、そして・・・

- 2014.12.23 腑に落ちない・・・

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

VHDLソース修正は続く

あけましておめでとうございます。

スキャンコンバータのソースの見直しをしています。外部クロックを逓倍するDCMのX68000起動時や解像度モード切り替え時の挙動をなんとかしようとしましたが、なかなか効果ある対処ができませんでした。そこで、発想を変え、DDR2メモリへまずはどんな解像度のものもそのままキャプチャさせ、表示側で水平解像度変更を行わせることにしました。

SVGAのピクセルクロックは40MHzですが、今度はこれの1/1.5、1/3の周波数のクロックを使ってDDRのメモリを読み出し表示させるのです(水平・垂直同期はSVGAのままに固定)。

で、外部クロックとは違い、安定したクロック50MHzでまずは1/1.5のクロックを作り動作試験をしました。その時の出力画像はこちら。絵が斜めになっています。 なんでこうなるか考え、あれやこれや半日いじって、やっと正常に表示するようになりました。その対応記録です。

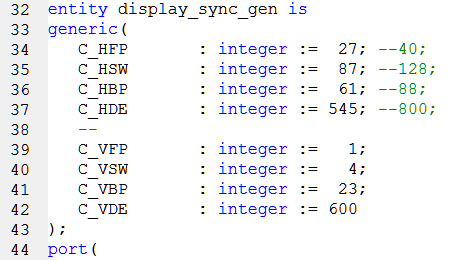

以下は表示タイミングを作る回路のVHDLソースの一部です。回路生成にあたって、ピクセルクロック換算で波形各部の長さを規定している部分で、SVGAのクロック40MHzの1.5分の1(正確にはDCMで作り出せたのは27.273MHzだったので、1.4667分の1)に合わせ、値を修正したところです。

C_HDEが水平表示期間を示し、800を545に直しているのですが、画像がおかしくなったのは、これが1多かったのが原因でした。C_HDEを544に減らし、合計値を合わせるため、C_HBP(バックポーチ)を逆に1足して生成し直すと正しく表示してくれました。HDMIの方も正常に表示してくれました。

こちらの回路生成では、X68000の起動時から誤動作することなく、512X512の画像をSVGA画像にしてくれました。解像度モード切り替え対応に向けて一歩前進です。

★★★ メインサイトへのリンク 「X68000改造室」★★★

スキャンコンバータのソースの見直しをしています。外部クロックを逓倍するDCMのX68000起動時や解像度モード切り替え時の挙動をなんとかしようとしましたが、なかなか効果ある対処ができませんでした。そこで、発想を変え、DDR2メモリへまずはどんな解像度のものもそのままキャプチャさせ、表示側で水平解像度変更を行わせることにしました。

SVGAのピクセルクロックは40MHzですが、今度はこれの1/1.5、1/3の周波数のクロックを使ってDDRのメモリを読み出し表示させるのです(水平・垂直同期はSVGAのままに固定)。

で、外部クロックとは違い、安定したクロック50MHzでまずは1/1.5のクロックを作り動作試験をしました。その時の出力画像はこちら。絵が斜めになっています。 なんでこうなるか考え、あれやこれや半日いじって、やっと正常に表示するようになりました。その対応記録です。

以下は表示タイミングを作る回路のVHDLソースの一部です。回路生成にあたって、ピクセルクロック換算で波形各部の長さを規定している部分で、SVGAのクロック40MHzの1.5分の1(正確にはDCMで作り出せたのは27.273MHzだったので、1.4667分の1)に合わせ、値を修正したところです。

C_HDEが水平表示期間を示し、800を545に直しているのですが、画像がおかしくなったのは、これが1多かったのが原因でした。C_HDEを544に減らし、合計値を合わせるため、C_HBP(バックポーチ)を逆に1足して生成し直すと正しく表示してくれました。HDMIの方も正常に表示してくれました。

こちらの回路生成では、X68000の起動時から誤動作することなく、512X512の画像をSVGA画像にしてくれました。解像度モード切り替え対応に向けて一歩前進です。

★★★ メインサイトへのリンク 「X68000改造室」★★★

PR

Web記事アップ

スキャンコンバータはその後、グラディウスの解像度256×256(縦方向は2度読み)にも対応でき、ここまでの取り組みを解説を含めWebの方にアップしておきました。 記事にも書きましたが、現在、解像度別のプログラムを1本にまとめるため四苦八苦しています。今の不具合を整理すると、

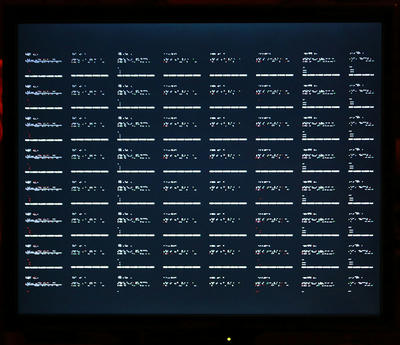

1 解像度変更のために必要なクロックを発生させるDCMを入れたコンバータを動作させておいてからX68000起動すると、Human68kの画面が次のようになる。

絵からすれば、取り込みクロックが35MHzX8.5=約300MHzとなるが、あり得ない状態だ。

原因不明。X68000を起動してからコンバータを動作させると正常に表示される。また、解像度768×512専用プログラムだとX68000起動時から正常に表示される。

2 X68000のプログラムで解像度変更が行われると、コンバータの動作が止まってしまう。

クロック中断によるFPGA内のDCMの動作停止が原因と思われる。いくつか対処を試みたが、未だ解決せず。

3 X68000の画面安定時に手動による解像度変更は可能だが、解像度判定回路を組んで自動変更させようとすると画面にノイズが走る。

などです。ほぼ毎日VHDLソースをいじってはいますが、なかなかうまくいきません。やはり完成まで時間がかかりそうです。

★★★ メインサイトへのリンク 「X68000改造室」★★★

1 解像度変更のために必要なクロックを発生させるDCMを入れたコンバータを動作させておいてからX68000起動すると、Human68kの画面が次のようになる。

絵からすれば、取り込みクロックが35MHzX8.5=約300MHzとなるが、あり得ない状態だ。

原因不明。X68000を起動してからコンバータを動作させると正常に表示される。また、解像度768×512専用プログラムだとX68000起動時から正常に表示される。

2 X68000のプログラムで解像度変更が行われると、コンバータの動作が止まってしまう。

クロック中断によるFPGA内のDCMの動作停止が原因と思われる。いくつか対処を試みたが、未だ解決せず。

3 X68000の画面安定時に手動による解像度変更は可能だが、解像度判定回路を組んで自動変更させようとすると画面にノイズが走る。

などです。ほぼ毎日VHDLソースをいじってはいますが、なかなかうまくいきません。やはり完成まで時間がかかりそうです。

★★★ メインサイトへのリンク 「X68000改造室」★★★

ユニバーサルボード

X68000の画像変更、進行中です。が、今回は別ネタ。

少し前になりますが、ヤフオクでX68000拡張スロット用ユニバーサルボードをゲットしました。もう絶対手に入らないと思っていた矢先の一品でした。

機能拡張には必須のアイテムですが、最初はこれに載せる予定だった画像表示変更回路は映像アンプBOXに収まりそうなので、しばらく出番はなさそうです。 何に利用しようかな。X68000は資料もあって基板上のICも既知のものが多く、手軽に改造が楽しめるので、夢が広がります。

★★★ メインサイトへのリンク 「X68000改造室」★★★

少し前になりますが、ヤフオクでX68000拡張スロット用ユニバーサルボードをゲットしました。もう絶対手に入らないと思っていた矢先の一品でした。

機能拡張には必須のアイテムですが、最初はこれに載せる予定だった画像表示変更回路は映像アンプBOXに収まりそうなので、しばらく出番はなさそうです。 何に利用しようかな。X68000は資料もあって基板上のICも既知のものが多く、手軽に改造が楽しめるので、夢が広がります。

★★★ メインサイトへのリンク 「X68000改造室」★★★

XVI基板の改造完了、そして・・・

XVIのメイン基板を改造し、16ビットカラー信号全てとドットクロック、水平・垂直同期信号をバッファを通して、IMAGE INコネクタに引き出しました。カラーイメージユニットは使えなくなりますが、もうNTSCの時代ではないし、使うことはないでしょう。74LS245などバッファICはIMAGE IN の入力バッファICの上に電源とGNDの端子を半田付けしておんぶさせました。

で、さっそくDDR2付きFPGA基板を接続し制御回路を生成し直して、512X512モードでのキャプチャを実験してみました。

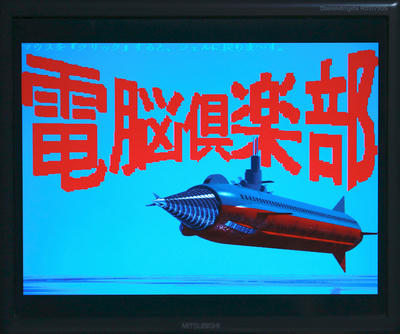

懐かしい「電脳倶楽部」のオープニング画像です。16ビットカラーできれいに表示してくれました。この時の標準解像度では、ドットクロックでそのまま取り込むと絵が縦長になる(アスペクト縦横比が2:3)ので、ドットクロックの19.43MHzをFPGAのDCMで1.5倍してそのタイミングで取り込みました。どうなるか少し不安でしたが、うまくいっているようです。DDR2も全域クリアしてから表示するようにしたので、絵の周りの柄模様も消えました。

標準解像度と高解像度のモード切替の自動化はまだうまくできません。解像度判別の理屈はあってるはずなんだけどなぜかな。VHDLソースを見直しています。

★★★ メインサイトへのリンク 「X68000改造室」★★★

で、さっそくDDR2付きFPGA基板を接続し制御回路を生成し直して、512X512モードでのキャプチャを実験してみました。

懐かしい「電脳倶楽部」のオープニング画像です。16ビットカラーできれいに表示してくれました。この時の標準解像度では、ドットクロックでそのまま取り込むと絵が縦長になる(アスペクト縦横比が2:3)ので、ドットクロックの19.43MHzをFPGAのDCMで1.5倍してそのタイミングで取り込みました。どうなるか少し不安でしたが、うまくいっているようです。DDR2も全域クリアしてから表示するようにしたので、絵の周りの柄模様も消えました。

標準解像度と高解像度のモード切替の自動化はまだうまくできません。解像度判別の理屈はあってるはずなんだけどなぜかな。VHDLソースを見直しています。

★★★ メインサイトへのリンク 「X68000改造室」★★★

腑に落ちない・・・

先にX68000の画像が限定モードではありながら、無事SVGA画像内に取り込めたことを報告しましたが、腑に落ちないことがあります。

実は、X68000の信号取り出し、FPGA基板への接続後、まずはその信号を直接アナログVGA端子に流す実験をしていましたが、色の乱れや文字パターンの一部が欠ける症状が発生していました。以下がその画像です。

取り出し信号がふらついているせいかもしれないと思い、RGB信号をドットクロックやその倍の信号でラッチさせたり、ラッチのタイミングをずらしたりしてもいっこうに改善の効果がみられず、なかばあきらめて、SVGA画像への取り込みをしてみたところ、なんときれいに取り込めているではありませんか。謎です。

★★★ メインサイトへのリンク 「X68000改造室」★★★

実は、X68000の信号取り出し、FPGA基板への接続後、まずはその信号を直接アナログVGA端子に流す実験をしていましたが、色の乱れや文字パターンの一部が欠ける症状が発生していました。以下がその画像です。

取り出し信号がふらついているせいかもしれないと思い、RGB信号をドットクロックやその倍の信号でラッチさせたり、ラッチのタイミングをずらしたりしてもいっこうに改善の効果がみられず、なかばあきらめて、SVGA画像への取り込みをしてみたところ、なんときれいに取り込めているではありませんか。謎です。

★★★ メインサイトへのリンク 「X68000改造室」★★★

カレンダー

フリーエリア

最新CM

[02/01 ぱち(管理人)]

[01/31 saku39]

[12/27 ぱち(管理人)]

[12/27 saku39]

[01/20 ぱち(管理人)]

最新記事

(01/13)

(12/31)

(12/30)

(11/26)

(11/25)

プロフィール

HN:

ぱち

性別:

非公開

ブログ内検索

最古記事

(01/13)

(01/19)

(01/20)

(01/21)

(01/22)